💻 Project Hardware/Software

Verilog/VHDL source code for VGA controller and pattern generator

Testbench and simulation files

Bitstream (.bit) and pin constraints for Spartan FPGA📄 Project Report

Complete documentation including VGA theory, block diagrams, code explanations, timing tables, and real-time output snapshots.🎥 Project Demo

Demonstration video showing pattern generation on a connected VGA display via FPGA.🚚 Free Delivery

Full digital project package delivered with organized folders and documentation.💬 Enhanced Customer Support

Help with FPGA setup, display configuration, design extension, and simulation assistance.

Project Overview

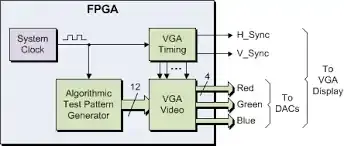

This project involves the design and FPGA implementation of graphical pattern generation using a VGA controller built with Hardware Description Language (HDL). By deploying the solution on a Spartan FPGA, users can render and display dynamic or static patterns on a VGA monitor in real time.

A VGA controller generates synchronization signals (horizontal and vertical sync) required to comply with VGA standards. The FPGA reads pixel or pattern data and uses the VGA timing mechanism to display graphical content on the screen. Patterns can include geometric shapes, color gradients, grids, or test visuals for calibration and diagnostics.

The project provides a hands-on introduction to digital video signal generation, frame buffer implementation, timing logic, and real-time display rendering. This system is ideal for applications in education, digital art, game development, testing equipment, and embedded HMI systems.

Project Objectives

Understand VGA Timing Specifications

Study VGA resolution (e.g., 640×480 @ 60Hz), timing diagrams, and signal structure.

Define the horizontal and vertical timing parameters (sync pulse, back porch, display time, front porch).Develop VGA Controller in HDL

Implement Verilog/VHDL modules to generate HSYNC and VSYNC signals.

Create counters for horizontal and vertical pixel tracking.Pattern Generation Logic

Design pixel color assignment logic based on current x-y coordinates.

Implement basic shapes (squares, circles), test bars, checkerboards, or animated visuals.Memory Integration (Optional)

Integrate ROM or block RAM for storing pattern data.

Enable dynamic pattern rendering from memory or input sources.Simulation and Timing Verification

Simulate VGA controller and pattern logic using tools like ModelSim or Vivado Simulator.

Analyze waveforms and timing alignment of sync and pixel data.FPGA Synthesis and Display Testing

Synthesize and deploy the design to a Spartan FPGA development board.

Connect to a VGA-compatible display and verify real-time output.Optimization and Customization

Enhance rendering with color blending, pattern switching, or coordinate-based animations.

Ensure timing meets 60Hz refresh rate and monitor compatibility.